## Architettura di un microprocessore

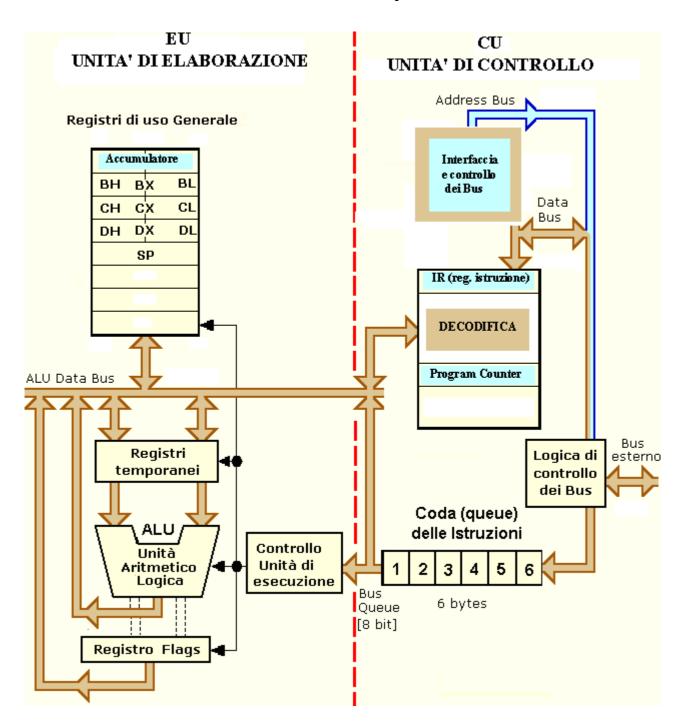

- Nell'architettura di una CPU, oltre alla necessaria temporizzazione (*timing*), si possono distinguere due sezioni:

- **unità di elaborazione** EU: contiene l'unità aritmetico logica (*ALU*); i registri ad uso generale tra cui l'*Accumulatore* con la funzione di memorizzare il risultato delle operazioni; il particolare registro di *Flag* (bit che segnalano condizioni che possono consentire un diverso flusso di esecuzione: il riporto di una somma, il risultato zero etc...); il particolare registro *SP* (Stack Pointer) che individua l'indirizzo iniziale dell'area di memoria (Stack Area) dove salvare lo stato della macchina (nel caso di cambio di contesto) consentendo di ripristinarlo quando si ritorna all'esecuzione del flusso principale.

- unità di controllo CU: usa registri speciali tra i quali il *PC* (Program Counter) che contiene l'indirizzo dell'istruzione che deve essere "eseguita" (compresa ed eseguita) ed il registro istruzione *IR* (che memorizza l'istruzione mentre la CPU la decodifica cioè la traduce da esadecimale in binario); la circuiteria per la *decodifica*, quella per memorizzare *code* di istruzioni (nel caso di architetture più evolute con tecnica prefetch) e quella per controllare il bus di sistema.

- Si distinguono due fasi nel funzionamento di una CPU con la più semplice architettura: la fase di *fetch* (interpretazione delle azioni da compiere) e quella di *execute* (esecuzione delle azioni). In particolare, durante la fase di *fetch* si realizzano le seguenti operazioni: il prelievo dell'istruzione dalla Ram, il caricamento nel registro istruzioni (IR) per la decodifica da esadecimale a binario e l'incremento del contatore di programma (Program Counter).

In architetture più evolute<sup>1</sup>, con tecnica prefetch o *prefetching*, la CPU può svolgere contemporaneamente la fase di fetch di una istruzione, e quella di execute della precedente già decodificata<sup>2</sup>.

In architetture parallele ancora più evolute<sup>3</sup> si distingue tra fase di *fetch* (prelievo e inoltro dell'istruzione nel registro istruzione IR), fase di *decodifica* con avanzamento del program counter e fase di *execute* durante le quali si usano risorse diverse e quindi la CPU può svolgere contemporaneamente la fase di fetch di una istruzione, quella di decodifica della precedente e quella di execute dell'istruzione già decodificata. Prende nome di tecnica pipeline o *pipelining* tale esecuzione *in parallelo* delle varie fasi di un'istruzione: mentre si esegue un'istruzione è già in corso l'acquisizione ed interpretazione delle successive.

<sup>&</sup>lt;sup>1</sup> Scheda di approfondimento in sito

<sup>&</sup>lt;sup>2</sup> Si usano code circolari (FIFO) da 6 a 128 byte.

<sup>&</sup>lt;sup>3</sup> Nel Pentium (come nel 68060 della Motorola) si usa la tecnica *pipeline superscalare* duplicando l'hardware e potendo svolgere 2 fasi di fetch nello stesso ciclo seguite da fasi duplicate di decodifica, read address (caricamento indirizzo operando cercando destinazione), read memory(passaggio valore operando), execute, write memory (caricamentoi in memoria del risultato)